SSD : Mọi điều bạn muốn biết – Phần 2

Trong ô nhớ Flash NAND cơ bản sự thay đổi lưu trữ hoặc không lưu trữ tại Cổng nổi , được đặt giữa hai lớp Oxit hoạt động như là lớp cách điện .

Trong kiểu đơn giản nhất của ô nhớ Flash NAND nếu không có dòng điện chạy qua giữa Nguồn ( Source ) và Ống ( Drain ) điều đó có nghĩa là Cổng nổi đã được nạp ( những điểm màu Lam là những điện tử ) và là đã được lập trình và giá trị nhị phân bằng 0 . Như hình trên .

Nếu có dòng điện chảy qua có nghĩa là Cổng nổi không được nạp và bị Xóa , đại diện là số 1 , hình trên bên phải .

MLC và TLC lưu trữ nhiều hơn một Bit cho mỗi ô nhớ

Ví dụ trên là của ô nhớ NAND SLC (Single Level Cell) . Nó chỉ có hai trạng thái đã được lập trình hoặc đã xóa và đại điện cho 1 Bit .

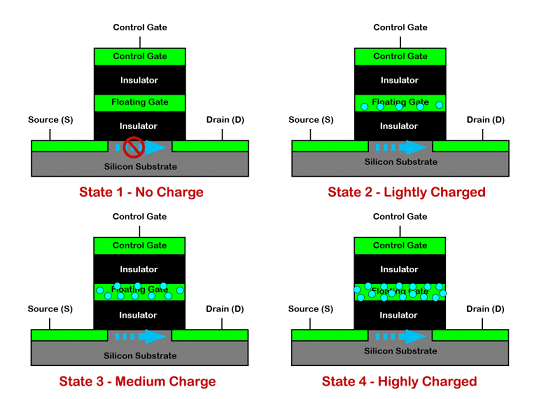

Ô nhớ Flash NAND MLC ( Multi Level Cell ) lưu trữ 2 Bit , với 4 mức trạng thái khác nhau . Để đạt được mục đích như vậy ô nhớ NAND MLC có thể cung cấp nạp cho Cổng nổi với 4 mức khác nhau và phải nhận biết được 4 mức trạng thái này .

Biểu đồ bên dưới cho thấy số lượng điện tử khác nhau ở Cổng nổi ( Floating Gate ) .

Trạng thái 1 không nạp , không có điện tử ở Cổng nổi .

Trạng thái 2 nạp nhẹ , số lượng điện tử tập trung ở Cổng nổi ít .

Trạng thái 3 nạp mức độ tầm trung , lượng điện từ dày đặc hơn trạng thái 2 .

Trạng thái 4 nạp cao , lượng điện tử dày đặc nhất .

Do có nhiều mức độ tập trung điện tử nên yêu cầu khi Đọc phải có độ chính xác cao hơn . Điều đó khiến cho NAND MLC Ghi chậm hơn so với SLC .

Ô nhớ Flash NAND TLC (Tri Level Cell) thậm chí còn phức tạp hơn nó lưu trữ 3-bit cho mỗi ô nhớ là yêu cầu 8 mức trạng thái khác nhau .

Cấu trúc NAND

Chuỗi và Mảng

Những phần trước chúng ta đã đề cập tới từng ô nhớ NAND riêng biệt , được dùng để lưu trữ 1- , 2- hoặc 3-bit . Trong phần này chúng ta sẽ nói tới bức tranh lớn hơn về những ô nhớ NAND được kết hợp với nhau thành những Chuỗi và những Mảng .

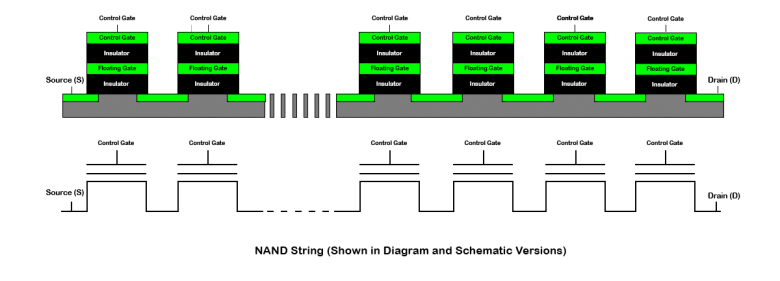

Một ô nhớ không có nhiều giá trị nhưng kết hợp chúng lại với nhau để cho phép lưu trữ được một số lượng lớn dữ liệu . Bước đầu tiên là kết hợp những ô nhớ NAND riêng biệt thành một Chuỗi NAND

Hình trên cho thấy Chuỗi NAND ở dạng biểu đồ . Những ô nhớ NAND được nối lại với nhau thành Chuỗi . Thông thường 32 hoặc 64 ô nhớ được nối lại với nhau .

Trong khi Chuỗi NAND có thể lưu trữ được 32-bit ( 4 Byte ) dữ liệu do đó những Chuỗi này lại kết hợp với nhau để trở thành những Mảng lớn hơn để lưu trữ được nhiều dữ liệu hơn .

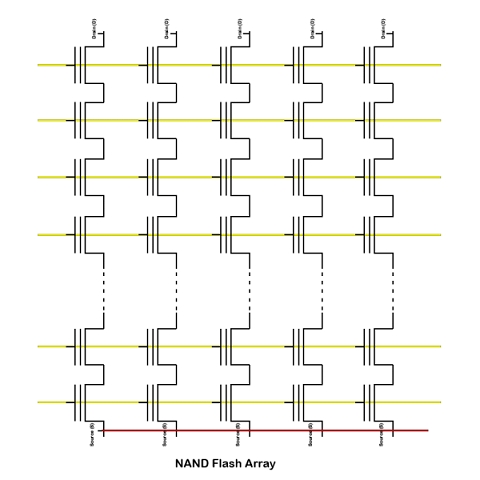

Hình trên cho thấy những Chuỗi NAND được lắp lại với nhau hình thành một Mảng . Lưu ý những kết nối thêm vào để làm cho những Chuỗi NAND hoạt động chặt chẽ hơn bên trong Mảng . Đường màu Đỏ nối những cổng Nguồn của những Chuỗi riêng biệt .

Đường màu Vàng nối tới Cổng điều khiển của Chuỗi NAND . Trong một Mảng , những Cổng điều khiển được nối với nhau theo chiều nằm ngang không theo chiều thẳng đứng .

Những đường Ống không thấy vì chúng sẽ được dùng riêng trong Mảng .

Trang và Khối ( Page & Block )

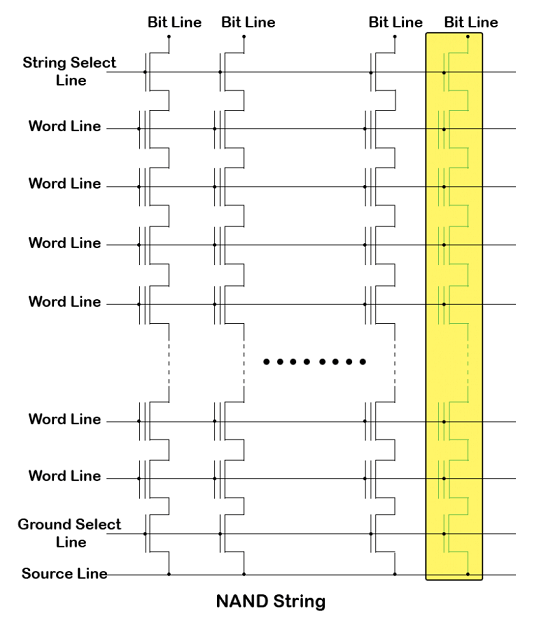

Hình trên cho thấy độ lớn của một mảng với những đường điều khiển và dữ liệu . Phần màu vàng bên phải là hình ảnh của một trong những Chuỗi .

Chuỗi là đơn vị nhỏ nhất để Đọc và thường bao gồm 32- hoặc 64 ô nhớ NAND . Tất cả các Chuỗi trong Mảng được nối với nhau ở điểm cuối tại đường SL ( Source Line ) và tại một điểm cuối khác của BL ( Bit Line ) .

Mỗi Chuỗi có hai cơ cấu điều khiển những ô nhớ bao gồm : SSL ( String Select Line ) và GSL ( Ground Select Line ) .

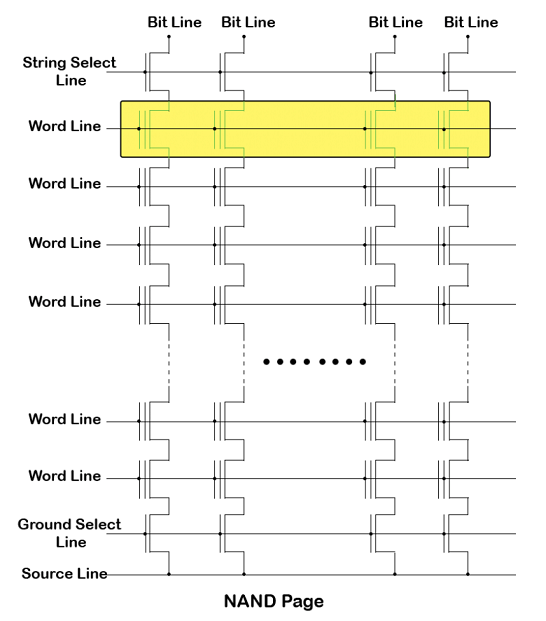

Hình trên cho thấy Trang NAND ( NAND Page ) được đánh dấu trong hình màu Vàng nằm ngang .

Page chia xẻ cùng Word Line và là đơn vị nhỏ nhất để Lập trình . Thông thường mỗi Page có ít nhất 32.768 ô nhớ ( 4KB ) , với nhiều thiết bị NAND mới hơn có kích thước trang lên tới 64KB hoặc 128KB ô nhớ .

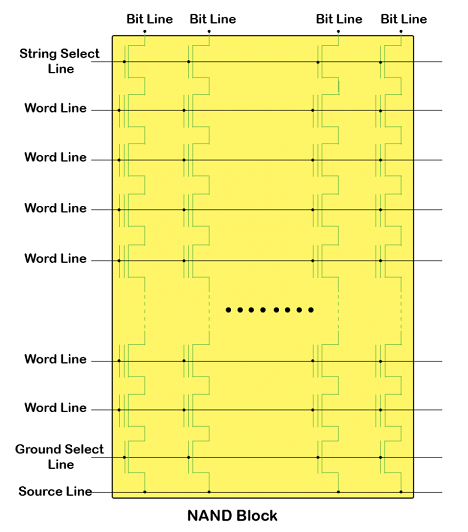

Hình màu Vàng trên cho thấy một Khối NAND ( Block ) .

Một Block là ma trận 2 chiều bao gồm những Page ( hàng ) và những Chuỗi ( String – cột ) Tổng số lượng Bit của một Block được tính bằng cách nhân số lượng Chuỗi và số lượng Page .

Tại Hội nghị 2014 Flash Memory Summit , Micron cho biết Page lớn nhất của mỗi Block là 512 và kích thước block lên tới 8MB .

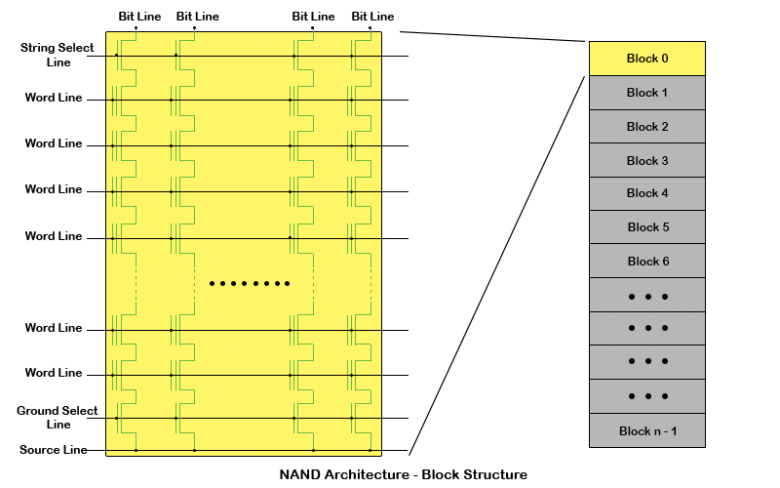

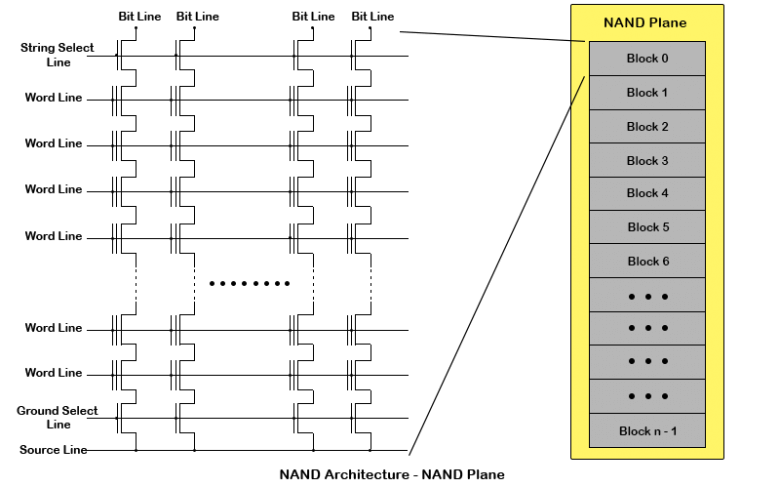

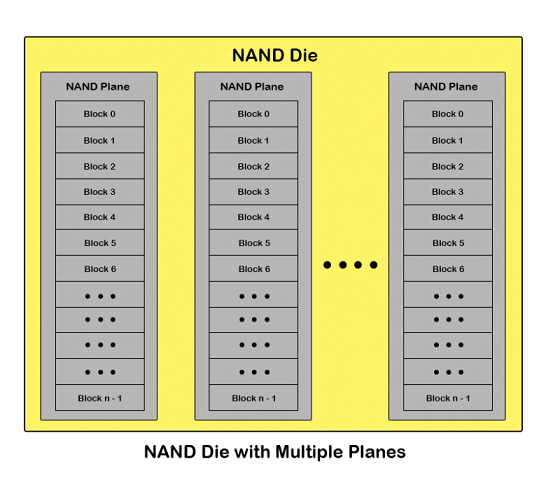

Plane và Die

Trong cấu trúc bộ nhớ NAND những khối kết hợp với nhau để tại thành Plane . Một hoặc nhiều Plane được nhóm lại với nhau để thành một Die như hình dưới . Có rất nhiều cấu hình của Die tùy theo thiết kế khác nhau mà những OEM cần

Một Die hoặc nhiều Die được xếp chồng lên nhau để tạo thành những định dạng chuẩn JEDEC thông dụng như TSOP , BGA …

Theo thời gian yêu cầu dung lượng lưu trữ ngày càng tăng nên có những cách mới để làm tăng mật độ lưu trữ . Một trong những công nghệ mới đang là mũi nhọn trong những năm dần đầy đó là bộ nhớ 3D .